Introduction: We start with some information on the importance of the BEOL processes. Then we will consider the metal choice of Al vs Cu as interconnect. Using these as examples, we will learn about the best way to combine different processes to achieve the goal of a robust process sequence. Integration literally means ‘unification’ or ‘putting together many things’. Here process integration means matching or combining different processes to obtain a finally ’passing’ or good chip. The ultimate purpose is to make the process robust so that many chips can be produced with maximum number of chips in good condition at the minimum cost.

Importance of BEOL: In the FEOL section, we learnt that the speed of a particular transistor is controlled by the gate length. Hence, when the size of the transistors decreased, the gate length decreased and the transistor speed increased. As an example, computers with 100 MHz speed were commercially available around 1995, and the speed continued to increase until it reached around 3 GHz. This is because with improvement in technology, it is possible to make transistors of smaller size. After about 3 GHz, a further increase in speed is not seen, at least in the commercially available chips. However, more ‘cores’ are made in a single chip and the functionality improves without an increase in speed. Why?

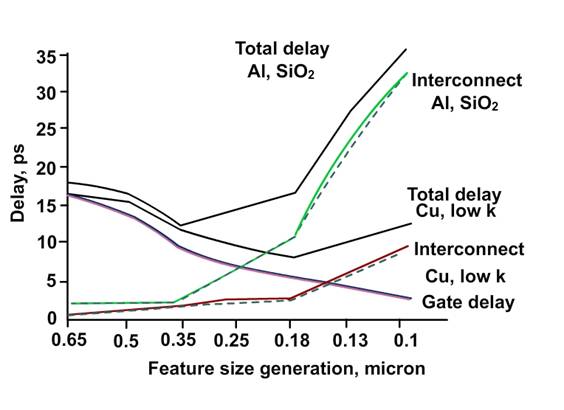

The transistors in the newer chips are smaller than the transistors of older chips. Thus the transistors can be switched on or off more quickly. But the signal from one transistor to another goes through the metal wires and the time delay is more in the newer chips. The delay is related to the resistance of the metal wire and the capacitance between the metal wires. This is also called as “RC delay”. (See Fig. 9.1)

When the transistors are made small, the connecting wires are also made small, which increases the metal resistance. When many transistors are packed closely in a chip, the metal wires connecting them also run close to each other. Thus the capacitance between the metal wires increases. This increases RC delay. Originally aluminum was used as interconnect and SiO2 was used as the insulator between the metal lines. The metal resistance can be decreased by replacing aluminum with copper. The capacitance can be decreased by replacing SiO2 with other materials with low-dielectric constant.

Fig 9.1. A qualitative plot illustrating the estimates of delay vs feature size. Notice that the feature size decreases along the abscissa (“X-axis”).

The transistors made in one layer, whereas the metal lines connecting them are made in many layers (~ 9 layers in some chips in 2011). The connections between the transistors are so complex that they can not be made in less number of layers. While making the transistors needs a complex sequence of processes, making a layer of interconnect is relatively less complex. As an example, the yield (i.e. success rate) of FEOL may be 95% . The yield of a single layer of interconnect (i.e .part of BEOL) may be 98%. But since there are 9 layers of BEOL, if we assume that each layer has a yield of 98%, the total BEOL yield is approximately (0.98)9 = 83%. Thus for the most modern chips, the BEOL part of the chip (i.e. interconnects and insulators) determine the speed of the chip and play a significant role in affecting the yield of the chip.

Marginal process vs robust process: A process is called marginal if a slight change in any of the conditions causes the process to change drastically. In contrast, a process is robust if it gives proper results even if there are minor changes in the conditions.

|